# Open-Source Radio Microcontroller for Fabrication

DESIGN DOCUMENT

Team Number: 27

Client/Adviser: Dr. Henry Duwe

Team Members/Roles: Ibram Shenouda – Analog Architecture Developer Noah Thompson – Analog Architecture Developer Nathan Stark – Digital Architecture Developer Nolan Eastburn – Digital Architecture Developer Ethan Kono – Security Architecture Developer Will Custis – Security Architecture Developer

Team Website: https://sdmay25-27.sd.ece.iastate.edu/

Revised: 12/4/2024/v1

# **Executive Summary**

Our goal with this project is to create a radio microcontroller unit (MCU) with all created artifacts being open-source. Then, if an individual desired to learn about how our radio MCU works, they could simply read our design and implementation artifacts. This makes our radio MCU unlike all others we found on the market, which are closed source. Closed source designs make it quite difficult for a user to understand how the unit works, which is what makes our design important for users who want to learn how a radio MCU works. Based upon this description, our design must meet the following key requirements:

- All created artifacts (design documents, test document, code, etc.) must be open-source

- All testing and design documentation must be understandable to an individual with a basic knowledge of circuits and embedded systems

- The design must allow for wireless communication using an open standard wireless communication protocol

- The design must be fabricated

- The design must be intuitive to use

- The design must interface to peripherals (servos, sensors, motors, etc.)

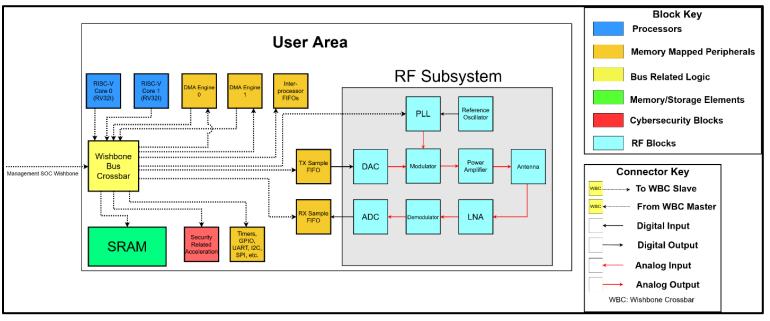

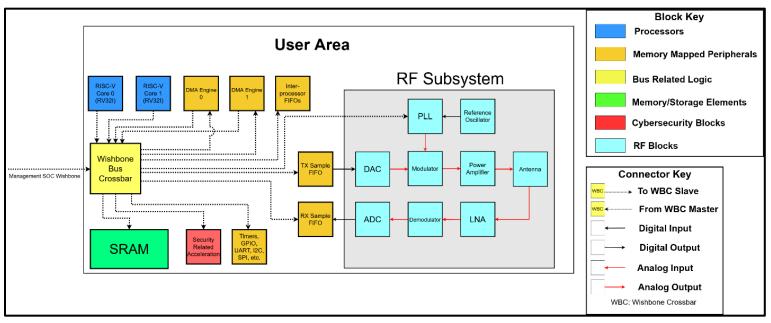

As required from our client, we will be using Caravel harness provided by the Efabless corporation to implement our design. The Caravel harness has a user area that can have a custom digital and analog design put in. The Caravel harness and the design we put in the user area will be laid out in the Skywater 130nm PDK, which Efabless has the means to fabricate in. This means we can fabricate the Caravel harness with our custom design in it to implement this MCU. For the design, we split it into two primary sections: digital and analog. The digital section contains all of the digital components that will execute instructions, transfer data, and interface with peripherals. The analog section will contain all the analog circuits required for RF communication. For the digital section, we are going to be implementing a RISC-V core, a DMA controller, an SRAM block, a wishbone crossbar to arbitrate all inter-component wishbone bus traffic, and a digital interface to the analog section. For the analog section, we will be implementing a PLL. These components alone will not be enough to enable RF communication, which violates one of our requirements. There is simply too much work for a single senior design team to implement a fully-functional radio MCU. However, implementing and fabricating these components will provide a good basis for future senior design teams to work on and the artifacts related to these components can still be studied by our users.

Currently, we have a design for the PLL, have researched SRAM generation, RISC-V core generation, have a prototype for the wishbone crossbar, and have created a simple project on the Caravel harness that is currently being fabricated. This provides us a sufficient baseline to begin implementation next semester in CPR E 4920. For our next steps on this project, we plan to take our research and start to implement the digital and analog components into the user area of the Caravel harness. Once we have some prototypes for the components implemented in the user area, we plan on running pre-fabrication tests and running the design through the OpenLane software, which will give us a layout that can be fabricated by Efabless. Based upon this summary, we believe that we are ready to implement our proposed design next semester and send it off for fabrication.

# Learning Summary

# Development Standards & Practices Used

We considered several engineering standards from IEEE. These include IEEE 802.15.1, 802.15.4, and 1481-2019. IEEE 802.15.1 outlines the requirements for the Bluetooth communication protocol, IEEE 802.15.4 outlines the requirements for the Zigbee communication protocol, and IEEE 1481-2019 outlines standards for verifying integrated circuit designs. While our project implementation will not contain everything necessary to make a functioning radio, the standards will help provide guidance when implementing the system to make sure that it can be easily extended to make a functional radio. In addition to these standards, we will also utilize best practices taught in courses and gained from experience in industry, such as self-checking testbenches to confirm digital designs work as intended. This will make verification easier, making it more likely that we will succeed in making a functional final product.

## Summary of Requirements

- The MCU shall be implemented using the Efabless Caravel Harness (constraint).

- The MCU shall implement the Zigbee communication stack.

- The MCU shall contain a radio subsystem.

- The MCU shall contain two independent RISC-V cores to execute user programs.

- The MCU shall contain two DMA engines.

- The MCU shall contain the following standard peripherals:

- processors.

- The MCU shall have software libraries that provide access to hardware functions.

- The MCU shall have a programming interface.

- The RF module shall able to transmit over the 915MHz ZigBee broadcast band with a 1MHz channel width.

• All Wishbone masters and slaves will use a 50 MHz reference clock which will be shared with the management SoC.

- 4 KiB of SRAM shall be provided for data storage.

- 4 KiB of SRAM shall be provided for instruction memory for the RISC-V processor.

- The MCU shall have a testing interface that enables a user to fully test the unit.

- The digital MCU peripherals shall be tested in a computer simulator to ensure correct behavior prior to fabrication.

- The MCU shall have a test plan to evaluate the characteristics of the system.

• Each piece of the RF module will be tested by sending their outputs to analog GPIO pads to read the waveforms. Some internal signals will be connected to the pads via transmission gates for testing.

- All the artifacts produced throughout the design of the MCU shall be open source (constraint).

- All the documentation shall be intuitive and understandable by individuals with a basic understanding of circuits, digital logic, and MCU usage (constraint).

- The design will fit into a die area of 2.92 mm x 3.52 mm (constraint).

# Applicable Courses from Iowa State University Curriculum

The following courses taught at Iowa State are relevant to this project.

| Course    | Relevance                               |

|-----------|-----------------------------------------|

| CPR E 281 | Basics of digital logic design and HDLs |

| CPR E 288 | Embedded systems programming in C       |

| CPR E 381 | More advanced digital hardware design,  |

|           | CPU architecture                        |

| E E 201   | Basics of electrical circuits           |

| E E 230   | More advanced electrical circuits and   |

|           | systems                                 |

| E E 330   | Integrated circuit design, testing, and |

|           | layout                                  |

| E E 465   | Digital VLSI                            |

| CYB E 331 | Cryptography                            |

# New Skills/Knowledge acquired that was not taught in courses

| Skill            | Relevance                                     |

|------------------|-----------------------------------------------|

| PLL design       | Key component in analog portion of the design |

|                  | 5                                             |

| ASIC fabrication | Design is going to be fabricated, design of   |

|                  | ASICs was taught, but not fabrication         |

|                  | specific                                      |

| NGSpice          | Simulator used for analog components          |

| OpenLane         | Hardening tool to convert HDL code into       |

|                  | digital logic layout                          |

# Table of Contents

| 1. | Introduc    | ction                                                                   | 13 |

|----|-------------|-------------------------------------------------------------------------|----|

| 1. | 1. Proble   | em Statement                                                            | 13 |

| 1. | 2. Intend   | ded Users                                                               | 13 |

|    | 1.2.1.      | ChipForge Co-Curricular                                                 | 13 |

|    | 1.2.2.      | Faculty                                                                 | 13 |

|    | 1.2.3.      | Radio Hobbyists                                                         | 14 |

| 2. | Require     | ments, Constraints, And Standards                                       | 14 |

| 2  | .1. Requi   | rements & Constraints                                                   | 14 |

|    | 2.1.1.      | Functional Requirements                                                 | 14 |

|    | 2.1.2.      | Testing Requirements                                                    | 15 |

|    | 2.1.3.      | Non-Functional Requirements                                             | 16 |

|    | 2.1.4.      | Resource Requirements                                                   | 16 |

| 2  | .2. Engin   | eering Standards                                                        | 16 |

|    | 2.2.1.      | Importance on Engineering Standards                                     | 16 |

|    | 2.2.2.      | IEEE 802.15.1 - Bluetooth Standard                                      | 16 |

|    | 2.2.3.      | IEEE 802.15.4 - LR-WPAN Standard (Zigbee)                               | 16 |

|    | 2.2.4.      | IEEE 1481-2019: Integrated Circuit (IC) Open Library Architecture (OLA) | 16 |

|    | 2.2.5.      | Incorporation into Project Design                                       | 17 |

| 3. | Project I   | Plan                                                                    | 17 |

| 3  | .1. Projec  | rt Management/Tracking Procedures                                       | 17 |

| 3  | .2. Task I  | Decomposition                                                           | 17 |

|    | 3.2.1.      | Research and Design                                                     | 17 |

|    | 3.2.2.      | Hardware Implementation                                                 | 18 |

|    | 3.2.3.      | Software Implementation                                                 | 21 |

|    | 3.2.4.      | Testing                                                                 | 21 |

| 3  | .3. 3.3 Pro | oject Proposed Milestones, Metrics, and Evaluation Criteria             | 22 |

|    | 3.3.1.      | Fall 24 Milestones                                                      | 22 |

|    | 3.3.2.      | Spring 25 Milestones                                                    | 22 |

| 3  | .4. Projec  | rt Timeline/Schedule                                                    | 23 |

|    | 3.4.1.      | Gantt Chart for Fall 24                                                 | 24 |

|    | 3.4.2.      | Gantt Chart for Spring 25                                               | 25 |

| 3.5. Ris | 1                                | 26 |    |

|----------|----------------------------------|----|----|

| 3.5.1.   | Unknown Design Tools             |    | 26 |

| 3.5.2.   | Limited Die Space                |    | 26 |

| 3.5.3.   | High Frequency Components        |    | 26 |

| 3.6. Pei | sonnel Effort Requirements       |    | 27 |

| 3.7. Ot  | her Resource Requirements        |    | 29 |

| 4. Desig | n                                |    | 29 |

| 4.1. De  | sign Context                     |    | 29 |

| 4.1.1.   | Broader Context                  |    | 29 |

| 4.1.2.   | Prior Work/Solutions             |    | 30 |

| 4.1.3.   | Technical Complexity             |    | 34 |

| 4.2. De  | sign Exploration                 |    | 35 |

| 4.2.1.   | Design Decisions                 |    | 35 |

| 4.2.2.   | ZigBee Wireless Protocol         |    | 35 |

| 4.2.3.   | Reducing Scope                   |    | 35 |

| 4.2.4.   | AES Encryption                   |    | 35 |

| 4.2.5.   | PLL Divider                      |    | 35 |

| 4.2.6.   | PLL Phase Frequency Detector     |    | 36 |

| 4.2.7.   | PLL Voltage Controlled Oscillate | r  | 36 |

| 4.2.8.   | PLL Charge Pump                  |    | 36 |

| 4.3. Ide | ation                            |    | 36 |

| 4.3.1.   | Wireless Protocols               |    | 36 |

| 4.3.2.   | Zigbee Wireless Protocol         |    | 36 |

| 4.3.3.   | BLE Wireless Protocol            |    | 36 |

| 4.3.4.   | Wi-Fi Wireless Protocol          |    | 37 |

| 4.3.5.   | LoRa Wireless Protocol           |    | 37 |

| 4.3.6.   | NB-IoT Wireless Protocol         |    | 37 |

| 4.3.7.   | PLL Divider Designs              |    | 37 |

| 4.3.8.   | First Order Delta Sigma          |    | 38 |

| 4.3.9.   | Dual Modulus                     |    | 39 |

| 4.3.10   | . PLL PFD Designs                |    | 40 |

| 4.3.11   | PLL VCO Designs                  |    | 42 |

| 4.3.12.     | 4.3.12.PLL Charge Pump Designs43            |    |  |  |  |  |  |

|-------------|---------------------------------------------|----|--|--|--|--|--|

| 4.3.13.     | Decision-Making and Trade-Off               | 45 |  |  |  |  |  |

| 4.3.14.     | Wireless Protocols                          | 45 |  |  |  |  |  |

| 4.3.15.     | PLL Divider Designs                         | 46 |  |  |  |  |  |

| 4.3 Propo   | 4.3 Proposed Design                         |    |  |  |  |  |  |

| 4.3.16.     | Overview                                    | 47 |  |  |  |  |  |

| 4.3.17.     | Detailed Design and Visual(s)               | 48 |  |  |  |  |  |

| 4.3.18.     | Analog Subsystem                            | 49 |  |  |  |  |  |

| 4.3.18.     | I. DAC                                      | 49 |  |  |  |  |  |

| 4.3.18.     | 2. PLL: Low Frequency Oscillator            | 49 |  |  |  |  |  |

| 4.3.18.     | 3. PLL: Phase Frequency Detector (PFD)      | 49 |  |  |  |  |  |

| 4.3.18.     | 4. PLL: Charge Pump and Filtering           | 50 |  |  |  |  |  |

| 4.3.18.     | 5. PLL: Voltage Controlled Oscillator (VCO) | 50 |  |  |  |  |  |

| 4.3.18.     | 6. PLL: Fractional N Divider                | 50 |  |  |  |  |  |

| 4.3.18.     | 7. Modulator                                | 50 |  |  |  |  |  |

| 4.3.18.     | 8. Power Amplifier                          | 50 |  |  |  |  |  |

| 4.3.19.     | Digital Subsystem                           | 50 |  |  |  |  |  |

| 4.3.19.     | 1. RISC-V Core                              | 50 |  |  |  |  |  |

| 4.3.19.     | 2. SRAM                                     | 51 |  |  |  |  |  |

| 4.3.19.     | 3. Security Acceleration                    | 51 |  |  |  |  |  |

| 4.3.19.     | 4. DMA Engine                               | 51 |  |  |  |  |  |

| 4.3.19.     | 5. Wishbone Crossbar                        | 51 |  |  |  |  |  |

| 4.4. Funct  | ionality                                    | 51 |  |  |  |  |  |

| 4.4.1.      | Areas of Concern and Development            | 52 |  |  |  |  |  |

| 4.5. Techr  | ology Considerations                        | 53 |  |  |  |  |  |

| 4.6. Desig  | n Analysis                                  | 53 |  |  |  |  |  |

| 5. Testing  |                                             | 53 |  |  |  |  |  |

| 5.1. Unit 7 | esting                                      | 53 |  |  |  |  |  |

| 5.1.1.      | Digital                                     | 53 |  |  |  |  |  |

| 5.1.1.1.    | Wishbone Crossbar                           | 54 |  |  |  |  |  |

| 5.1.1.2.    | VexRISCV Core                               | 54 |  |  |  |  |  |

| 5.1.1.3.    | DMA Engine                                  | 54 |  |  |  |  |  |

| 5.1.1.4. TX Sample FIFO                         | 54 |

|-------------------------------------------------|----|

| 5.1.1.5. Security Acceleration                  | 54 |

| 5.1.2. Analog                                   | 54 |

| 5.1.2.1. Phase Frequency Detector (PFD)         | 54 |

| 5.1.2.2. Charge Pump and Filtering              | 55 |

| 5.1.2.3. Voltage Controlled Oscillator (VCO)    | 55 |

| 5.1.2.4. Fractional N Divider                   | 55 |

| 5.2. Interface Testing                          | 55 |

| 5.2.1. Digital                                  | 55 |

| 5.2.2. Analog                                   | 55 |

| 5.2 Integration Testing                         | 55 |

| 5.3. System Testing                             | 56 |

| 5.3.1. Digital                                  | 56 |

| 5.3.2. Analog                                   | 56 |

| 5.3 Regression Testing                          | 56 |

| 5.3.3. Digital                                  | 56 |

| 5.3.4. Analog                                   | 56 |

| 5.4. Acceptance Testing                         | 56 |

| 5.4.1. Digital                                  | 57 |

| 5.4.1.1. Wishbone Crossbar pt. 1                | 57 |

| 5.4.1.2. VexRISCV Core                          | 57 |

| 5.4.1.3. Security Acceleration                  | 57 |

| 5.4.1.4. DMA Engine                             | 57 |

| 5.4.1.5. DMA Engine/Wishbone Crossbar pt. 2     | 57 |

| 5.4.1.6. System Testing                         | 57 |

| 5.4.2. Analog                                   | 58 |

| 5.4.2.1. PLL Testing Architecture               | 58 |

| 5.4.2.2. PLL Measurements and Characterizations | 58 |

| 5.5. Security Testing                           | 59 |

| 5.6. Results                                    | 59 |

| 6. Implementation                               | 59 |

| 6.1. Wishbone Crossbar                          | 59 |

| 6.2. Seven-Segment Controller                                                                                                                                                                                                                  | 60                         |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|--|--|

| 7. Ethics and Professional Responsibility                                                                                                                                                                                                      | 60                         |  |  |  |  |  |  |  |

| 7.1. Areas of Professional Responsibility/Codes of Ethics                                                                                                                                                                                      | 60                         |  |  |  |  |  |  |  |

| 7.2. Four Principles                                                                                                                                                                                                                           | 62                         |  |  |  |  |  |  |  |

| 7.3. Virtues                                                                                                                                                                                                                                   | 63                         |  |  |  |  |  |  |  |

| 7.3.1. Responsibility                                                                                                                                                                                                                          | 63                         |  |  |  |  |  |  |  |

| 7.3.2. Respect                                                                                                                                                                                                                                 | 63                         |  |  |  |  |  |  |  |

| 7.3.3. Flexibility                                                                                                                                                                                                                             | 63                         |  |  |  |  |  |  |  |

| 7.3.4. Individual Virtue Assessment                                                                                                                                                                                                            | 63                         |  |  |  |  |  |  |  |

| 7.3.4.1. Ibram Shenouda                                                                                                                                                                                                                        | 63                         |  |  |  |  |  |  |  |

| 7.3.4.2. Noah Thompson                                                                                                                                                                                                                         | 64                         |  |  |  |  |  |  |  |

| 7.3.4.3. Nathan Stark                                                                                                                                                                                                                          | 64                         |  |  |  |  |  |  |  |

| 7.3.4.4. Nolan Eastburn                                                                                                                                                                                                                        | 64                         |  |  |  |  |  |  |  |

| 7.3.4.5. Ethan Kono                                                                                                                                                                                                                            | 65                         |  |  |  |  |  |  |  |

| 7.3.4.6. William Custis                                                                                                                                                                                                                        | 65                         |  |  |  |  |  |  |  |

| 8. Closing Material                                                                                                                                                                                                                            | 65                         |  |  |  |  |  |  |  |

| 8.1. Conclusion                                                                                                                                                                                                                                | 65                         |  |  |  |  |  |  |  |

| 8.2. References                                                                                                                                                                                                                                | 66                         |  |  |  |  |  |  |  |

| 8.3. Appendices                                                                                                                                                                                                                                | 67                         |  |  |  |  |  |  |  |

| 8.3.1. Security Analysis                                                                                                                                                                                                                       | 67                         |  |  |  |  |  |  |  |

| 8.3.1.1. Attacks & Vulnerabilities in Microcontrollers 67                                                                                                                                                                                      |                            |  |  |  |  |  |  |  |

| 8.3.1.2. Countermeasures and Solutions for Vulnerabilities in Microcontrollers                                                                                                                                                                 | s 68                       |  |  |  |  |  |  |  |

| 8.3.1.3. Attacks & Vulnerabilities in Radio Frequency Modules 69                                                                                                                                                                               |                            |  |  |  |  |  |  |  |

| 8.3.1.4. Countermeasures and Solutions for Vulnerabilities in Microcontrollers                                                                                                                                                                 | s 70                       |  |  |  |  |  |  |  |

| 8.3.1.5. Conclusion 70                                                                                                                                                                                                                         |                            |  |  |  |  |  |  |  |

| 9. Team 71                                                                                                                                                                                                                                     |                            |  |  |  |  |  |  |  |

| <ul> <li>9.1. Team Members</li> <li>9.2. Required Skill Sets for Your Project</li> <li>9.3. Skill Sets covered by the Team</li> <li>9.4. Project Management Style Adopted by the team</li> <li>9.5 Initial Project Management Roles</li> </ul> | 71<br>71<br>72<br>72<br>72 |  |  |  |  |  |  |  |

| 9.5. Initial Project Management Roles729.6. Team Contract72                                                                                                                                                                                    |                            |  |  |  |  |  |  |  |

# Figures

| Figure 1: Research and Design Task Decomposition      |

|-------------------------------------------------------|

| Figure 2: Hardware Implementation Task Decomposition2 |

| Figure 3: Software Implementation Task Decomposition2 |

| Figure 4: Testing Task Decomposition2                 |

| Figure 5: Fall 24 Gantt Chart                         |

| Figure 6: Spring 25 Gantt Chart 2                     |

| Figure 7: First Order Delta Sigma                     |

| Figure 8: Dual Modulus Divider                        |

| Figure 9: PLL Diagram                                 |

| Figure 10: Phase Frequency Detector4                  |

| Figure 11: Phase Frequency States4                    |

| Figure 12: PFD gain without dead zones4               |

| Figure 13: PFD gain with Dead Zone4                   |

| Figure 14: Dead Zones Jitter                          |

| Figure 15: Ring Oscillator                            |

| Figure 16: Current-Starved Ring Oscillator            |

| Figure 17: PLL Charge Pump & Loop Filter4             |

| Figure 18: Charge Pump with added buffers4            |

| Figure 19: Full Implementation4                       |

| Figure 20: Full Implementation                        |

| Figure 21: PLL Architecture                           |

| Figure 22: Minimum Design Implementation5             |

| Figure 23: PLL Test Diagram                           |

# Tables

| Table 1: Personnel Effort Requirements                            | . 27 |

|-------------------------------------------------------------------|------|

| Table 2: Broader Design Context                                   | . 30 |

| Table 3: Market Research                                          | 31   |

| Table 4: Areas of Professional Responsibility and Codes of Ethics | .60  |

| Table 5: Four Ethical Principles                                  | . 62 |

## 1. Introduction

#### **1.1. PROBLEM STATEMENT**

Many radio microcontroller units (MCUs) exist on the market today; however, their designs are closed source. This makes it difficult for users of radio MCUs such as the ISU ChipForge cocurricular, faculty, and radio hobbyists to learn about radio microcontrollers without reverse engineering the unit due to the designs not being publicly available. It is important that they learn about radio communication now as wireless connections are becoming more common compared to their wired counterparts. To address this, our team is designing an open-source radio MCU. This will provide anyone who desires to learn about how a radio MCU works with all the documentation and implementation details, including how we designed and implemented in our unit. In addition, our implementation can be fabricated through the Efabless Corporation, which allows users to physically use and analyze the radio MCU on top of being able to look at design documents. Having this radio MCU be open-source enables users to make their own modifications to the design, which is something an individual cannot do with closed source units. This further promotes learning and creates opportunities for individuals to be innovative with the base radio MCU design.

#### **1.2.** INTENDED USERS

#### 1.2.1. ChipForge Co-Curricular

Chip Forge is a co-curricular at Iowa State University (ISU) that primarily focuses on the design and fabrication of chips through the Efabless Corporation. The members of Chip Forge consist of undergraduate and graduate students at ISU as well as faculty advisors. All members of Chip Forge have an interest in chip fabrication and desire to learn more about it through project development and experimentation. Based upon their interests, the ChipForge members need an open-source radio MCU that they can see the designs for, fabricate the design, and then use the MCU in the lab. This will allow them to dive deep into how a radio frequency (RF) subsystem works on an MCU as well as use this MCU has a component in any projects they work on. This provides a much better learning experience than attempting to reverse-engineer an existing closed source radio MCU, which would prove to be quite difficult and not clear. Finally, we hope that the ChipForge members can take the radio MCU design and build upon it to meet their needs. Since the original design can be fabricated, the ChipForge members can make whatever modifications they see fit for their applications and learn tons about radio MCUs along the way.

#### 1.2.2. Faculty

Some courses at Iowa State University utilize microcontrollers for labs, such as CPR E 288. Once fabricated and tested, faculty could use the open-source MCU for lab assignments in place of existing options. Faculty teaching these courses need a reliable way to teach students about MCUs with good documentation and tooling support. Good documentation and tools are essential since this will likely be used for undergraduate students. Documentation and tools would also reduce the time that faculty need to spend changing existing lab experiments should they adopt the new MCU. There are several potential advantages of the open-source MCU over existing ones. These include the ability to tailor the hardware to course requirements, such as adding additional functionality not commonly implemented in other commercially available products. Additionally, for cybersecurity focused courses, faculty could provide students the opportunity to study in detail

a wireless device from the hardware level in the lab, which would be a valuable learning experience not able to be replicated with closed-source designs.

#### 1.2.3. Radio Hobbyists

Radio hobbyists are usually interested in unique features and documentation/tooling and need MCUs that enable them to communicate with other devices in an easy way without a lot of setup. If one examines commercial MCUs that sell well amongst hobbyists, they are typically low-cost, have good tools and documentation, and have several connectivity features that allow hobbyists to connect them to common devices. Due to the low volume of the production, competing on price will be difficult, but tools and documentation is going to be a central focus of the project, and unique features are possible due to the open-source nature of the project. Furthermore, for hobbyists with a larger budget, our design could serve as a starting point to develop their own MCU tailored to their specific application.

# 2. Requirements, Constraints, And Standards

#### 2.1. REQUIREMENTS & CONSTRAINTS

#### 2.1.1. Functional Requirements

- The MCU shall be implemented using the Efabless Caravel Harness (constraint).

o All digital and analog components shall be compatible with the Skylake 130nm technology that the Caravel platform supports (constraint).

- The MCU shall implement the Zigbee communication stack.

- o The MCU shall be able to connect to Zigbee-compatible devices.

o The MCU shall adhere to the security protocols defined in the Zigbee communication stack.

- The MCU shall contain a radio subsystem.

- o The radio subsystem shall support multiple operating frequencies.

- o The radio subsystem shall support multiple modulation schemes.

- o The radio subsystem shall be able to transmit and receive information to/from other radios.

- The MCU shall contain two independent RISC-V cores to execute user programs.

- The MCU shall contain two DMA engines.

- The MCU shall contain the following standard peripherals:

- o GPIO, UART, I2C, configurable timers, and SPI.

- o The peripherals must have an easy interface for use and configuration (constraint).

- The MCU peripherals shall be memory-mapped and accessible to the RISC-V processors.

- The MCU shall have software libraries that provide access to hardware functions.

- The MCU shall have a programming interface.

- The programming interface shall be over a serial connection to the MCU.

- o The programming interface shall have a stand-alone application that users run on their PCs to program the MCU.

• The programming interface shall be intuitive to use, such that an individual with basic MCU programming knowledge can easily program the MCU (constraint).

• The RF module shall able to transmit over the 915MHz ZigBee broadcast band with a 1MHz channel width.

o The carrier signal will be generated by an analog PLL frequency synthesizer to 915MHz using a reference oscillator.

o The PLL will be able to step 1MHz between 902 and 928MHz to land at every frequency band.

o The input signal from the processor will go through a DAC before being modulated with the carrier signal using quadrature phase shift keying

o The modulated signal will be sent to a power amplifier and transmitted from an antenna.

o The transmit power shall be between -15dBm to 3odBm (less than 1000mW)

o The PLL shall have a settling time of less than or equal to 170us <u>ATSAMR30M18A</u>

o The PLL output will have phase noise less than -91dBm/Hz at a 32 MHz offset.

• All Wishbone masters and slaves will use a 50 MHz reference clock which will be shared with the management SoC.

- 4 KiB of SRAM shall be provided for data storage.

- 4 KiB of SRAM shall be provided for instruction memory for the RISC-V processor.

#### 2.1.2. Testing Requirements

- The MCU shall have a testing interface that enables a user to fully test the unit. o The testing interface should provide electrical connections to the following components in the MCU for testing:

- RISC-V cores, DMA engines, peripheral interfaces, PLL

• The digital MCU peripherals shall be tested in a computer simulator to ensure correct behavior prior to fabrication.

- The MCU shall have a test plan to evaluate the characteristics of the system.

- o The test plan shall provide steps to test the electrical characteristics of the system.

- Supply voltage, power consumption, output voltages, slew rates

- The test plan shall provide steps to test the MCU peripherals via software.

- Transmit and receive for communication peripherals (I2C, SPI, UART).

- Correct divider, counter, and comparator behavior for timer.

- Correct input/output functionality for GPIO.

• Each piece of the RF module will be tested by sending their outputs to analog GPIO pads to read the waveforms. Some internal signals will be connected to the pads via transmission gates for testing.

o The PLL will have part if not all of its loop filter outside the chip for area optimization.

o The PLL will have its divider, PFD, reference oscillator, and VCO simulated and characterized using the layout derived from the caravel board.

The wave forms can then be used to confirm the components behave as expected.

#### 2.1.3. Non-Functional Requirements

• All the artifacts produced throughout the design of the MCU shall be open source (constraint).

• All the documentation shall be intuitive and understandable by individuals with a basic understanding of circuits, digital logic, and MCU usage (constraint).

#### 2.1.4. Resource Requirements

• The design will fit into a die area of 2.92 mm x 3.52 mm (constraint).

#### 2.2. ENGINEERING STANDARDS

#### 2.2.1. Importance on Engineering Standards

• Engineering standards are important to ensure safety, reliability, and compatibility with other products and protocols. Standards also ensure that the creation and manufacturing of products meets sets of requirements that are deemed necessary to meet several different qualifications.

#### 2.2.2. IEEE 802.15.1 - Bluetooth Standard

• This standard defines the physical and medium access control layers for wireless communication. The Bluetooth standard is used worldwide for low power wireless communication devices across short range radio frequency connectivity, which is important for our project as we are implementing a short range and low radio frequency device through the caravel and Efabless process. Its standards will be important to take into consideration since our design implements an RF (radio frequency) module as well.

#### 2.2.3. IEEE 802.15.4 - LR-WPAN Standard (Zigbee)

• This standard specifies low-rate wireless personal area network operations, network stack, model, and foundational network layers for the physical and MAC networking layers. It is the basis for the ZigBee standard that our project group is utilizing. It also specifies communication for low-rate wireless devices and is intended to provide solid foundations in networking for said wireless devices. This standard applies to our project as the ZigBee protocol outlines the details of operating a ZigBee device so that they are compatible with existing devices. This includes details of the physical and MAC layers of the network stack, which are necessary for reliable communication.

#### 2.2.4. IEEE 1481-2019: Integrated Circuit (IC) Open Library Architecture (OLA)

• This standard provides the analysis for designers to analyze timing, signal integrity, logic behavior, and power consumption across different technologies within a certain accuracy. This standard is relevant to our project since it notes proper timing processes which are essential for the correct operation of the digital components of our microcontroller unit and the RF module.

#### 2.2.5. Incorporation into Project Design

• General principles of power consumption and timing closure will be taken into consideration for our project design and implementation, as it is important for both the MCU and RF module we are designing. The general protocols and principles for Bluetooth and ZigBee will also be utilized and based around because all other low-rate wireless devices follow the same set of requirements and protocols. Incorporating those standards specifically into our project will be necessary across the network stack for connectivity with other devices that use the same protocols and standards.

## 3. Project Plan

#### 3.1. PROJECT MANAGEMENT/TRACKING PROCEDURES

This project will be managed using a Waterfall approach. This was chosen because we have a small set of deliverables with a lot of interdependence that are required to be completed by a deadline with little flexibility. Waterfall will help make sure that each part of the project (requirements, design, implementation, verification) are all completed in order. Additionally, documentation is a key part of the project, and Waterfall methodology typically results in more comprehensive documentation than Agile, the other approach that was considered. This stems from the fact that Agile focuses on functionality over documentation as defined in the Agile Manifesto. Since the project will span multiple senior design teams, it is more acceptable to trade off functionality for better documentation, since poorly documented functions would likely cause delays and confusion among future design teams.

The project will use Git as the version control system for code created for the project and a repository hosted on the Iowa State Gitlab server. This was chosen since Git provides a lot of functionality for managing different feature development and dealing with conflicts, and the Iowa State Gitlab is already set up for easy collaboration. Issue tracking will be done using Trello, since it is free and allows for custom categories to easily classify issue status. Project communication is currently utilizing a Discord server since it is free, allows different channels to discuss different aspects of the project, and allows for voice and video calls for remote collaboration.

#### 3.2. TASK DECOMPOSITION

The task decomposition for the project was broken into four main categories, with each having several subcategories to further break down tasks so they can be more easily measured. This will allow for actionable tasks that can easily be assigned to team members so everyone knows what they should be doing.

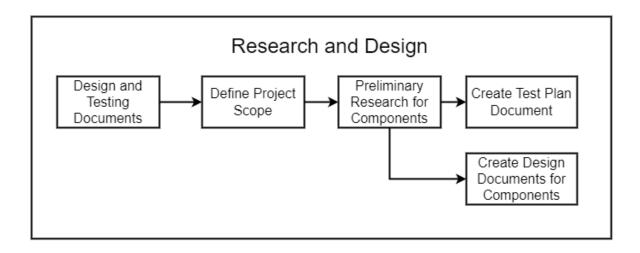

#### 3.2.1. Research and Design

The primary deliverables expected from this portion of the project are the test plan document and the documentation for the components of the system (both hardware and software). The test plan will outline the bring up tests necessary to confirm the chip functions correctly after it is fabricated.

This will need a high level of detail, since these tests will be carried out by people not directly involved with the design process. The documentation for individual components is also important, since the design will be used by a variety of people, including undergraduate students with limited experience, so understanding how each component of the system functions is critical for the chip to be useful.

#### Figure 1: Research and Design Task Decomposition

#### 3.2.2. Hardware Implementation

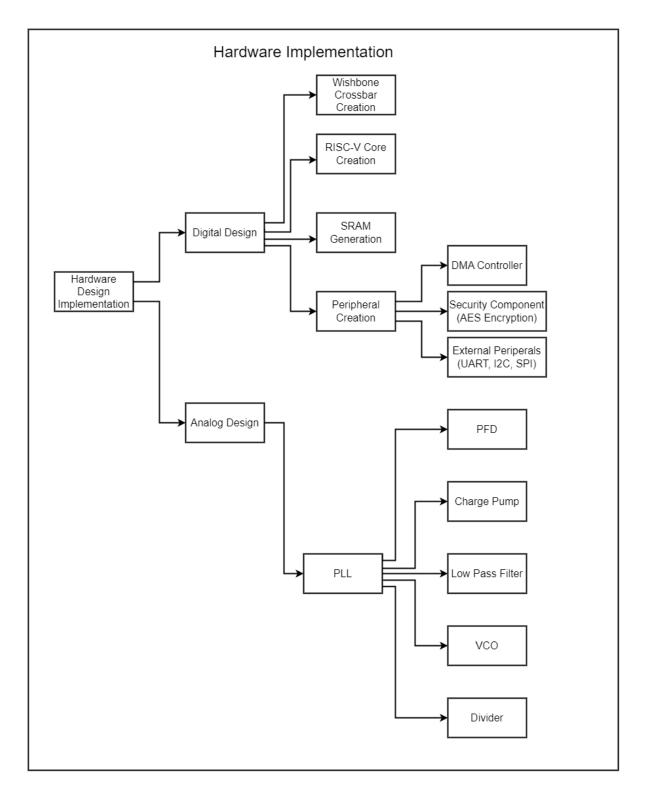

The hardware implementation is split into two primary categories, analog and digital design. These two will be developed and tested separately and combined during integration to create the final system.

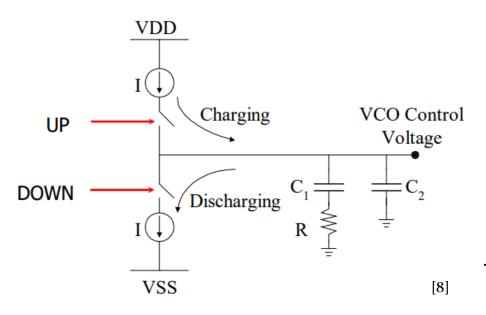

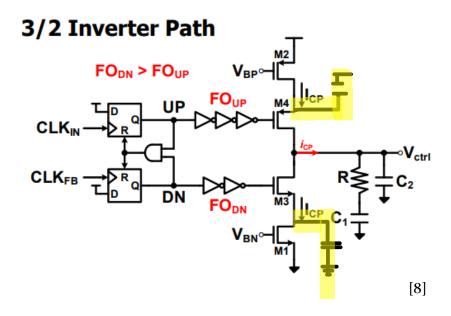

The analog design will primarily consist of a PLL, which in turn is made up of a phase detector, charge pump, low pass filter, voltage-controlled oscillator, and a divider. Each of these components will be designed and tested individually before being integrated together to form the final PLL. In future iterations of the project, the PLL will make up an RF subsystem for transmitting and receiving data.

The digital design will consist of a Wishbone crossbar, RISC-V core, SRAM, DMA controller, security acceleration, and external peripherals. The Wishbone crossbar will arbitrate access to memory mapped peripherals in the design and will be created by hand and may change in the future due to concerns about area usage. The RISC-V core will be generated using a project called VexRISCV that provides optimized cores with good performance along with customization options. This core will be responsible for running user software. The SRAM will be generated using OpenRAM, an open-source tool for creating SRAM layouts. The SRAM will serve primarily as data storage for the RISC-V core, with smaller blocks being used for instruction memory or FIFOs to send/receive data. The DMA controller will help to offload work from the RISC-V core when transferring data to/from various peripherals. This will allow users to encrypt and decrypt data more efficiently than doing it in software by providing hardware capable of performing these operations. Finally, the external peripherals will provide a way for the user application to

communicate with other devices using protocols such as I2C, SPI, or UART. This will let users interact with other devices, such as sensors, nonvolatile storage, or other microprocessors.

Figure 2: Hardware Implementation Task Decomposition

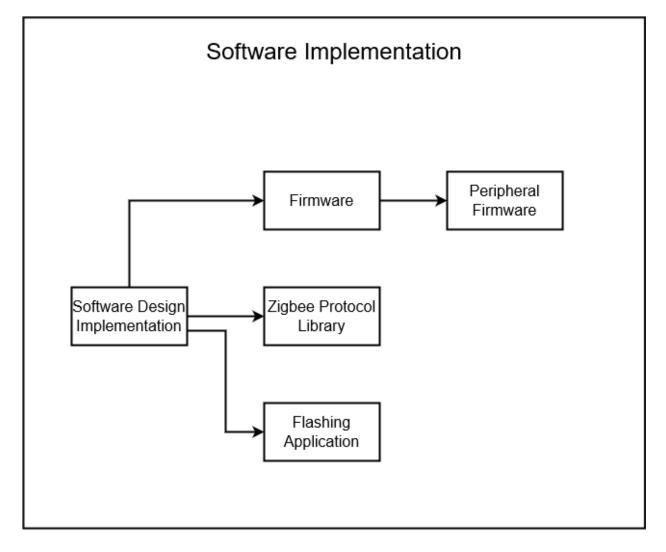

#### 3.2.3. Software Implementation

There are three primary software deliverables for the project. These are the peripheral firmware, the Zigbee protocol library, and the flashing application. The peripheral firmware will provide easy access to the digital peripherals described in the previous section. This will help make the design more accessible to users, since they will not have to directly interact with memory-mapped registers and can instead use high level functions in their application. The Zigbee protocol library will help make user application development easier by providing functionality that implements lower levels of the Zigbee protocol so users can focus on the high-level transfer of data. Finally, the flashing application will provide an easy way for users to upload their compiled programs to the RISC-V core for execution.

#### Figure 3: Software Implementation Task Decomposition

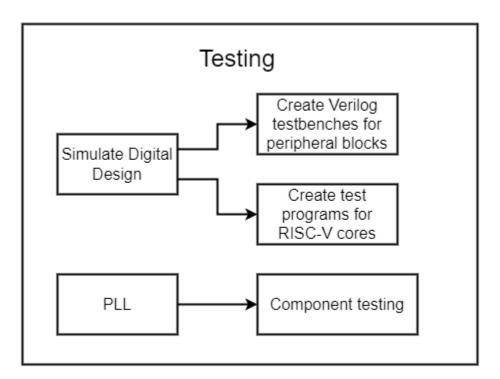

#### 3.2.4. Testing

Testing of the various components of the design will be essential to ensuring that the chip functions properly. There are three primary types of testing that will be performed. Verilog

testbenches for the digital peripherals will help to ensure that the blocks work correctly in isolation, which will help to eliminate sources of error during integration. Test C programs for the RISC-V processor will provide a means of system-level testing and will make sure that the system functions as intended. Finally, analog component testing in simulation for the PLL will make sure that the PLL is functioning as expected, and can be tested after fabrication to ensure the fabricated version meets specifications.

#### Figure 4: Testing Task Decomposition

#### 3.3. 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

#### 3.3.1. Fall 24 Milestones

- Design document finished

- Initial hardware designs finalized

- Specific Implementations of each PLL components

- Baseline implementations of peripherals

- o RISC-V core design

- Initial test plan

- o Defined expected behavior of each component

- System to test component behavior

#### 3.3.2. Spring 25 Milestones

- Hardware components created

- o All baseline implementations created and building

- Initial testing complete

- o Hardware components tested as a system in simulation/on FPGA

- Test plan created

- $\circ$   $\;$  Test cases for after fabrication to evaluate electrical characteristics and behavior of the device

- Test cases should cover all peripherals and electrical characteristics

#### 3.4. PROJECT TIMELINE/SCHEDULE

Our full project timeline and schedule are captured in our Gantt charts shown on the next pages. Due to the complexity of our project, many of the tasks will need to be shifted to the end of Fall or Spring of next year. We will only have a single deliverable after the Spring semester, which will contain a partial implementation of our design as well as all of the design and testing documentation.

### 3.4.1. Gantt Chart for Fall 24

| Weeks/Task                 |                              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|----------------------------|------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Project Scope              |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Research available tools   | OpenRAM                      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | RISC-V Core Generation       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Wishbone Crossbar Creation |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| RISC-V Core Creation       |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| SRAM Generation            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| DMA Controller             |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Security Component         | AES 128-bit Encryption       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| External Peripherals       |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Fabrication                |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Radio Frequency Components | Bluetooth                    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | ZigBee                       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Phase Locked Loop (PLL)    | Research                     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Phase Frequency Detector     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Charge Pump                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | low Pass Filter              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Voltage Controlled Oscilator |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Divider                      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Testing                      | 1 |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Create Design Documents    |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Create Testing Documents   |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Testbench Creation         | Peripherals                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | RISC-V Core                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Key:                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Initial Design               |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Research                     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Implementation               |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                            | Fabrication                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

Figure 5: Fall 24 Gantt Chart

### 3.4.2. Gantt Chart for Spring 25

|                                 |                              | Spring |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|---------------------------------|------------------------------|--------|--------|--------|------|---|---|---|---|---|----|----|----|----|----|----|----|

| Weeks                           | /Task                        | 1      | 2      | 3      | 4    | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Project Scope                   |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Research available tools        | OpenRAM                      |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | RISC-V Core Generation       |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Wishbone Crossbar Creation      |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| <b>RISC-V</b> Core Creation     |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| SRAM Generation                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| DMA Controller                  |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Security Component              | AES 128-bit Encryption       |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| External Peripherals            |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Fabrication                     |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Radio Frequency Components      | Bluetooth                    |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | ZigBee                       |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Phase Locked Loop (PLL)         | Research                     |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | Phase Frequency Detector     |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | Charge Pump                  |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | low Pass Filter              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | Voltage Controlled Oscilator |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | Divider                      |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | Testing                      |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Create Design Documents         |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| <b>Create Testing Documents</b> |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

| Testbench Creation              | Peripherals                  |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 | RISC-V Core                  |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        | K      | ey:    |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        | Initia | Desig  | n    |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        | Resea  |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        | Imple  | menta  | tion |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        |        |        |      |   |   |   |   |   |    |    |    |    |    |    |    |

|                                 |                              |        | Fabri  | cation |      |   |   |   |   |   |    |    |    |    |    |    |    |

Figure 6: Spring 25 Gantt Chart

#### 3.5. RISKS AND RISK MANAGEMENT/MITIGATION

#### 3.5.1. Unknown Design Tools

#### Risks

- Our team has no experience with Caravel and the Efabless process.

- Some tools have known issues that may cause delays.

#### Mitigation

- We are Currently working with members of ISU Chip Forge to learn how to design for the Caravel Board and avoid known issues.

- We will use available IP from the Efabless marketplace when possible.

#### 3.5.2. Limited Die Space

#### Risks

- The die is 2.92mm x 3.52mm, this means we may not be able to fit everything we want on the chip.

- Challenging to accurately evaluate the amount of space on the die.

#### Mitigation

- We have created a list of components for a minimum viable product that must be included.

- We can remove lower priority components from the design should die space become an issue.

- If necessary, some components can be accessed via a breakout board.

- Based on our testing, about 300KB of RAM would fill the chip.

#### 3.5.3. High Frequency Components

#### Risks

- High frequency component behavior is difficult to predict prior to simulation.

- Simulation may reveal that divider creates too much spurring for the PLL to create a usable signal.

#### Mitigation

- We plan to characterize each individual component through simulation and use that data to characterize the system. This will allow us to quickly pinpoint a component that is not meeting its requirements and revise its design.

- As a backup, we have investigated an alternative divider design that eliminates spurring at the cost of greater noise.

### 3.6. PERSONNEL EFFORT REQUIREMENTS

Below is an effort analysis for each of our tasks listed in our Gantt chart:

| Task                                      | Hours<br>(estimate) | Justification                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Define Project Scope                      | 80                  | The scope of this project is quite large and there<br>are many different components we can<br>implement. This will take substantial effort.                                                                                                                                                                                                         |

| Research OpenRAM                          | 15                  | There exists good documentation for OpenRAM<br>and it utilizes generation scripts. This will only<br>take about a week of effort.                                                                                                                                                                                                                   |

| Research RISC-V Core<br>Generation        | 15                  | There exists good documentation for the Vex<br>RISC-V generator and the generation is done via<br>scripts. This will only take around a week of<br>effort.                                                                                                                                                                                          |

| Wishbone Crossbar<br>Creation             | 50                  | This component is inherently complicated since<br>it must multiplex many different wishbone<br>interfaces. This will take a large amount of effort.                                                                                                                                                                                                 |

| RISC-V Core Creation                      | 50                  | Although the core itself will be generated, an<br>interface must be defined for the core such that it<br>can interact with the rest of the design and be<br>programmed. This is complex since we have<br>many components in our design, and we must<br>find a way to supply the core with a program.<br>This will require a large amount of effort. |

| SRAM Generation                           | 40                  | The SRAM will be generated, which is not too<br>difficult, but it will need to be integrated into our<br>design and have an interface over the wishbone<br>bus, which makes this complex. This will require<br>a large amount of work.                                                                                                              |

| Create DMA Controller                     | 60                  | The DMA controller is an inherently complex<br>component that will take a decent amount of<br>research to understand how to create. In<br>addition, we will have to create an interface for<br>this component so it can interact with the rest of<br>our design, which is complex. This will take a<br>substantial amount of work.                  |

| Create AES 128-bit<br>Encryption Hardware | 40                  | This hardware will require research to<br>implement, but there is good documentation and<br>known hardware solutions. The main difficulty<br>will be incorporating this into the rest of the<br>design, which is not trivial. This will take a large<br>amount of effort.                                                                           |

| Create External<br>Peripherals            | 80                  | We are including many peripherals in our final<br>design, each of which have well documented<br>designs, but can be complicated. Since we are<br>implementing many peripherals and need to<br>create an interface for them so they can interact                                                                                                     |

#### Table 1: Personnel Effort Requirements

|                                             |    | with the rest of the design, this will require a substantial amount of effort.                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fabrication                                 | 30 | Substantial amount of enort.The fabrication itself won't be done by us sinceEfabless will be doing the fabrication, but gettingthe design ready for fabrication will bechallenging. We have to make sure that all of ourhardware designs are compatible with the 130nmprocess, which can be checked using toolsprovided by Efabless. Depending on how manyissues we have when we run the checker tools,this may take a large amount of effort. |  |

| Research PLL                                | 20 | The PLL is inherently complex, but there exists<br>good documentation of hardware<br>implementations. So, this will require a few<br>weeks of effort.                                                                                                                                                                                                                                                                                          |  |

| Research Phase Frequency<br>Detector        | 20 | analog research complexity note<br>The analog design for the RF module will be<br>complicated since many different analog<br>components are required to create each<br>component. Good documentation exists, but<br>many of our team members have not had prior<br>experience designing these analog components.<br>Therefore, it will take a few weeks to fully<br>research each component.                                                   |  |

| Research Charge Pump                        | 20 | See "analog research complexity note"                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Research Low-Pass Filter                    | 20 | See "analog research complexity note"                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Research Voltage<br>Controlled Oscillator   | 20 | See "analog research complexity note"                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Research Divider                            | 20 | See "analog research complexity note"                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Create a Testing<br>Environment for the PLL | 50 | Since the PLL is a complicated component,<br>creating the testing environment for it will be<br>complicated as well. There are many different<br>waveforms we need to see and analyze and it is<br>not trivial to setup an interface to accomplish<br>this. Therefore, this will take a large amount of<br>effort.                                                                                                                             |  |

| Design Each PLL<br>Component                | 80 | Create each component of the PLL on the Caravel board, then extract its parasitics to be used for simulation.                                                                                                                                                                                                                                                                                                                                  |  |

| Simulate Each PLL<br>Component              | 30 | Simulate each component, testing expected behavior, loop characteristics and signal characteristics.                                                                                                                                                                                                                                                                                                                                           |  |

| Finalize PLL Design                         | 50 | Review and revise the design based on<br>simulations. Determine PLL characteristics to be<br>tested after fabrication.                                                                                                                                                                                                                                                                                                                         |  |

| Create Design Documents                     | 80 | The design documents are quite large and will be<br>edited throughout the course. This will take a<br>substantial amount of effort.                                                                                                                                                                                                                                                                                                            |  |

| Create Testing Documents                    | 80 | The testing documents will be quite large and must contain detailed instructions to test our                                                                                                                                                                                                                                                                                                                                                   |  |

|                                   |    | many components. This will take a substantial amount of work.                                                                                                                                                                              |

|-----------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Create Peripheral<br>Testbenches  | 60 | Since we have many peripherals, each of which<br>can be complicated, creating testbenches for the<br>peripherals will take a large amount of work.                                                                                         |

| Create RISC-V Core<br>Testbenches | 60 | Due to the complexity of a RISC-V core, creating<br>a solid testbench will be very difficult. There are<br>many different signals we would need to capture<br>and analyze in a meaningful way. This will take a<br>large amount of effort. |

#### 3.7. OTHER RESOURCE REQUIREMENTS

We currently require a testing platform to test our designs and a means to fabricate our design. Currently, the ISU co-curricular ChipForge provides a fully-functional testing platform, and we have an agreement with Efabless to fabricate our design on a given date. With these resources and documentation, we can find online and at ISU (mainly through professors, classes, and literature), we have all we need to implement our design or parts of our design due to time constraints.

# 4. Design

#### 4.1. DESIGN CONTEXT

All radio MCUs currently available are closed source and use proprietary architectures. This makes it more difficult for members of ChipForge, a co-curricular at ISU, and professors doing research to understand their inner workings and tailor them to their specific needs. Our design will focus on being easy to understand as well as open-source, which will allow users to look into the implementation and customize it for their own needs if they have access to the fabrication resources. This will also be supplemented with in-depth documentation, to make the design easy to understand for people with a basic level of knowledge of electrical and computer systems.

#### 4.1.1. Broader Context

The primary community targeted by our design is college students and professors, since they would likely benefit the most from having access to an open-source radio MCU. Since the product we are creating will likely be lower performance as a tradeoff for being open-source, it is unlikely to impact the microcontroller industry significantly. The biggest societal need being addressed is the need for transparency in microcontroller design, something that is not addressed by many major companies in the space.

| Area              | Description                                 | Examples                     |

|-------------------|---------------------------------------------|------------------------------|

| Public health,    | Our project will benefit people who are     | Extensible design            |

| safety, and       | college students and professors by          | Documentation allows for     |

| welfare           | providing a learning platform that is       | students with basic          |

|                   | capable of performing a variety of tasks    | knowledge to use             |

|                   | often asked of MCUs. It is unlikely to      |                              |

|                   | have a significant impact on companies      |                              |

|                   | or organizations that already have a        |                              |

|                   | foothold in the MCU market.                 |                              |

| Global, cultural, | The academic community has a strong         | Open-source code             |

| and social        | tradition of sharing resources and          | Documentation                |

|                   | information, and the open-source nature     | • Contributing to an ISU co- |

|                   | of our design helps to continue this        | curricular                   |

|                   | tradition by making our work available      |                              |

|                   | to be built on by others.                   |                              |

| Environmental     | There are two potential sources of          | Fabrication impact           |

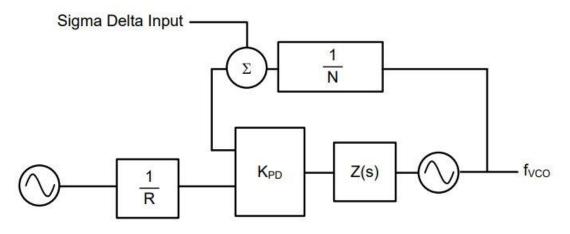

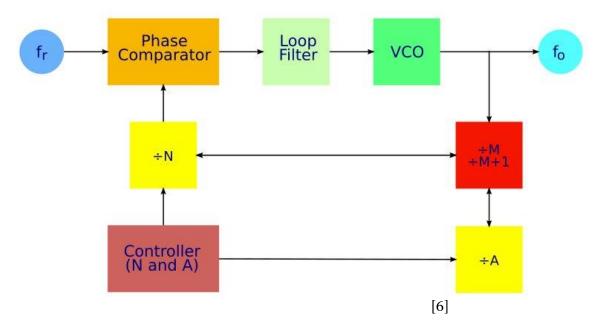

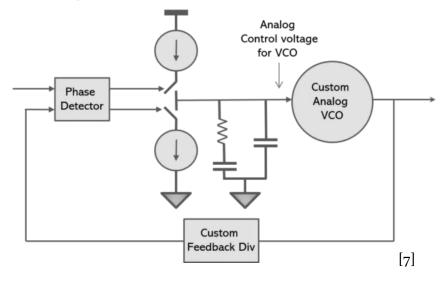

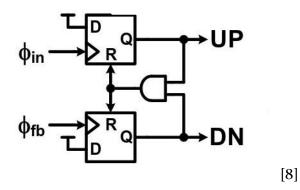

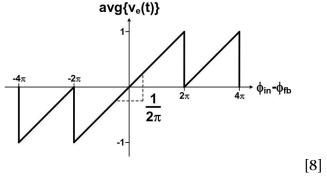

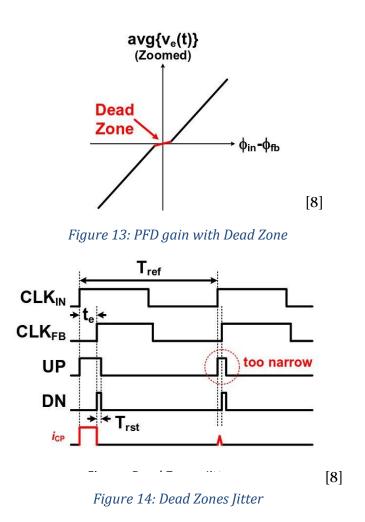

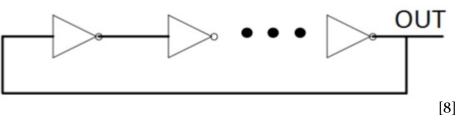

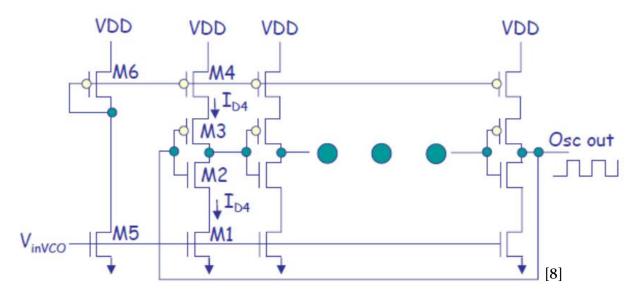

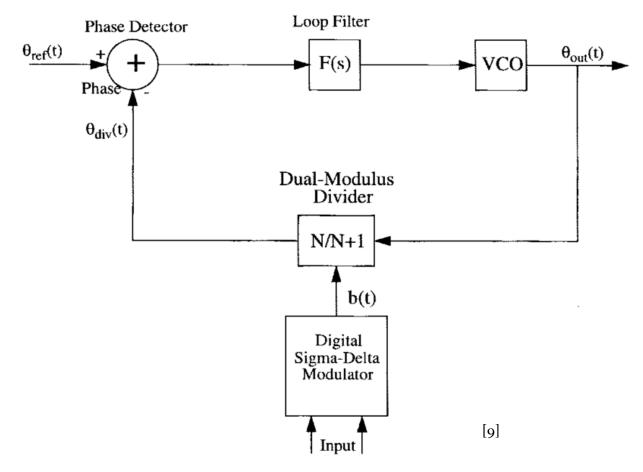

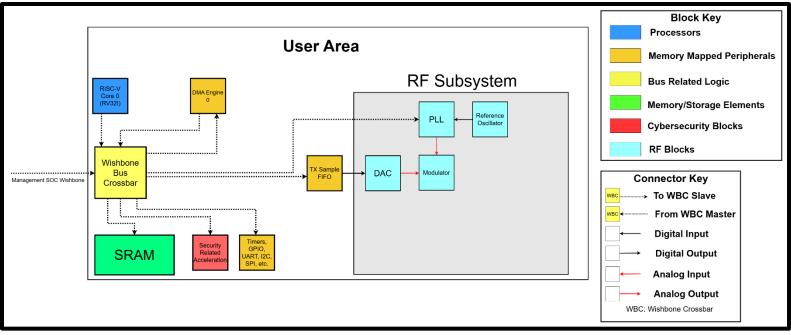

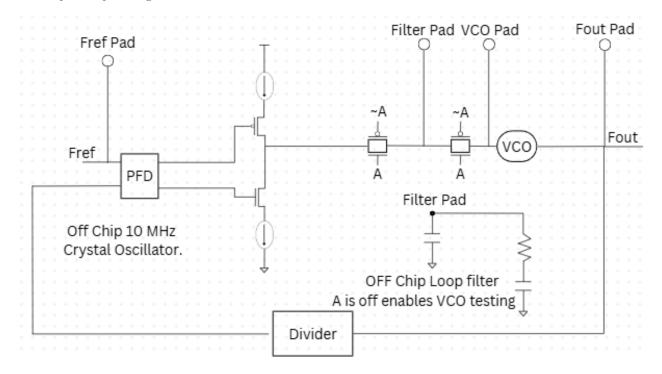

|                   | environmental impact for the project, the   | Power consumption during     |