# Project Planning Lightning Talk

sdmay25-27

Nathan Stark, Nolan Eastburn, Noah Thompson, Will Custis, Ethan Kono, Ibram Shenouda

Client/Advisor: Dr. Duwe

#### **Project Overview**

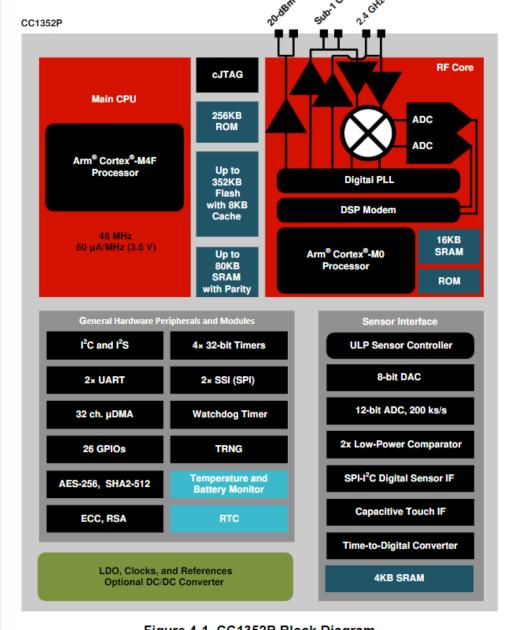

- Design a microcontroller with radio communication capabilities

- Open-source

- Can be fabricated

- Will be used by ISU ChipForge group, possibly faculty and hobbyists

- Designed using the Caravel platform from Efabless

- Inspired by the TI CC1352P (block diagram shown to the right)

Figure 4-1. CC1352P Block Diagram

# Project Management Style

- Using a Waterfall approach

- Useful since project has a small set of large deliverables

- Challenging to do incremental development using Agile with so many interconnected components

#### Task Decomposition

- Four primary categories

- Documents

- Design document

- Test plan document

- Hardware Implementation

- Digital components

- Analog components

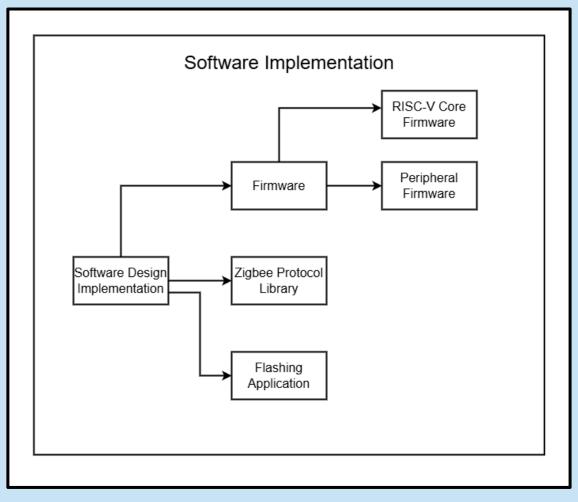

- Software Implementation

- Zigbee protocol

- Flash application

- Firmware

- Testing

- Digital simulation

- Test programs

- Analog simulation

1 of 3 of our task decomposition graphics

### Key Milestones and Metrics

- Design document finished

- Hardware components created

- All baseline implementations created and building

- Initial testing complete

- Hardware components tested as a system in simulation/on FPGA

- Test plan created

- Test cases for after fabrication to evaluate electrical characteristics and behavior of the device

- Test cases should cover all peripherals and electrical characteristics

Gantt chart for fall period on the next slide

|                             | Fall                         |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|-----------------------------|------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

| Weeks/Task                  |                              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Project Scope               |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Research available tools    | OpenRAM                      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | RISC-V Core Generation       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Wishbone Crossbar Creation  |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| RISC-V Core Creation        |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| SRAM Generation             |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| DMA Controller              |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Security Component          | AES 128-bit Encryption       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| <b>External Peripherals</b> |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Fabrication                 |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Radio Frequency Components  | Bluetooth                    |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | ZigBee                       |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Phase Locked Loop (PLL)     | Research                     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | Phase Frequency Detector     |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | Charge Pump                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | low Pass Filter              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | Voltage Controlled Oscilator |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | Divider                      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | Testing                      |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Create Design Documents     |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Create Testing Documents    |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

| Testbench Creation          | Peripherals                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             | RISC-V Core                  |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|                             |                              |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

# Key Risks

- Unknown design tools

- Design tools are different from those used in ISU courses

- Some tools have known issues that may cause delays

- Limited die space (2.92 mm x 3.52 mm)

- May not be possible to fit everything we want

- Difficult to evaluate prior to initial implementation

### Risk Mitigation

- Unknown design tools

- Currently working to get acquainted with tools

- Dr. Duwe has pointed us towards some people who have more experience with tools

- Limited die space

- Have created list of components in minimum viable product

- If die space becomes issue, can strip out components incrementally

#### Conclusion

- There are four primary tasks to complete for the project

- Tasks are somewhat dependent on each other

- Will require good coordination to stay on schedule

- Risks associated with unfamiliar tools and process limitations

- Doing more research to understand, have options to reduce impact